PDP-8/L Renovering

Re: PDP8 Renovering

Den teletypen ser hygglig ut, jag skulle åtminstone vilja ha pappersstativet som ligger framför. Det saknas på min. Jag tar gärna hela.

- anders_bzn

- Inlägg: 5927

- Blev medlem: 17 december 2008, 19:22:18

- Ort: Kävlinge

- Kontakt:

Re: PDP8 Renovering

Hm, det stativet saknar jag också. Nåväl jag hittar ett sen.

Jag tar gärna stansen i vilket fall!

Jag tar gärna stansen i vilket fall!

Re: PDP8 Renovering

Kom att tänka på...

Detta skulle ju kunna intressera några här.

Har nästan funderat på att ta en semster i UK under den tiden...

Detta skulle ju kunna intressera några här.

Har nästan funderat på att ta en semster i UK under den tiden...

Just a last reminder that the DEC Legacy Event is on in four weeks

time. We've got some interesting kit lined up - several PDP8s,

MicroPDP 11, VT100, MV2, several other VAXen, Alpha, IA64 boxes,

terminals etc. Stephen Hoffman will be giving a remote talk and Steve

Davidson will be helping create a HECnet based DECnet cluster, and

hopefully giving us a little history of his time a DEC Engineering.

You are most welcome to come and join us, it's always a fun weekend

and a good place to make friends with people sharing a common interest

and history.

More details here: http://www.declegacy.org.uk

Kind regards, Mark.

Re: PDP8 Renovering

Åh, nu blir jag sugen på att åka. Jag skulle gärna höra Hoffman. Det är nog lite för dyrt tyvärr :/

- anders_bzn

- Inlägg: 5927

- Blev medlem: 17 december 2008, 19:22:18

- Ort: Kävlinge

- Kontakt:

Re: PDP8 Renovering

Ja, just nu är det inte läge för en sådan resa. Hoppas man får en ny möjlighet. Det verkar vara trevligt på något sätt.

Re: PDP8 Renovering

anders_bzn, den där moderna stansen vill jag inte skänka bort. Jag kanske var lite otydlig med det.

Du får komma med ett bud.

Jag är lite kluven hur jag ska göra med ASR-33'an på bild.

Jag har ytterligare en som är komplett, men den misstänker jag att råttorna har varit på, så man kanske behöver någon ressrvdel.

Den där pappersplåten kan jag hursomhelst avvara och även andra delar om ni behöver.

Du får komma med ett bud.

Jag är lite kluven hur jag ska göra med ASR-33'an på bild.

Jag har ytterligare en som är komplett, men den misstänker jag att råttorna har varit på, så man kanske behöver någon ressrvdel.

Den där pappersplåten kan jag hursomhelst avvara och även andra delar om ni behöver.

- anders_bzn

- Inlägg: 5927

- Blev medlem: 17 december 2008, 19:22:18

- Ort: Kävlinge

- Kontakt:

Re: PDP8 Renovering

säter: Jag förstår. Jag behöver den inte, så jag får fundera på saken. Antar att den inte försvinner snabbt...

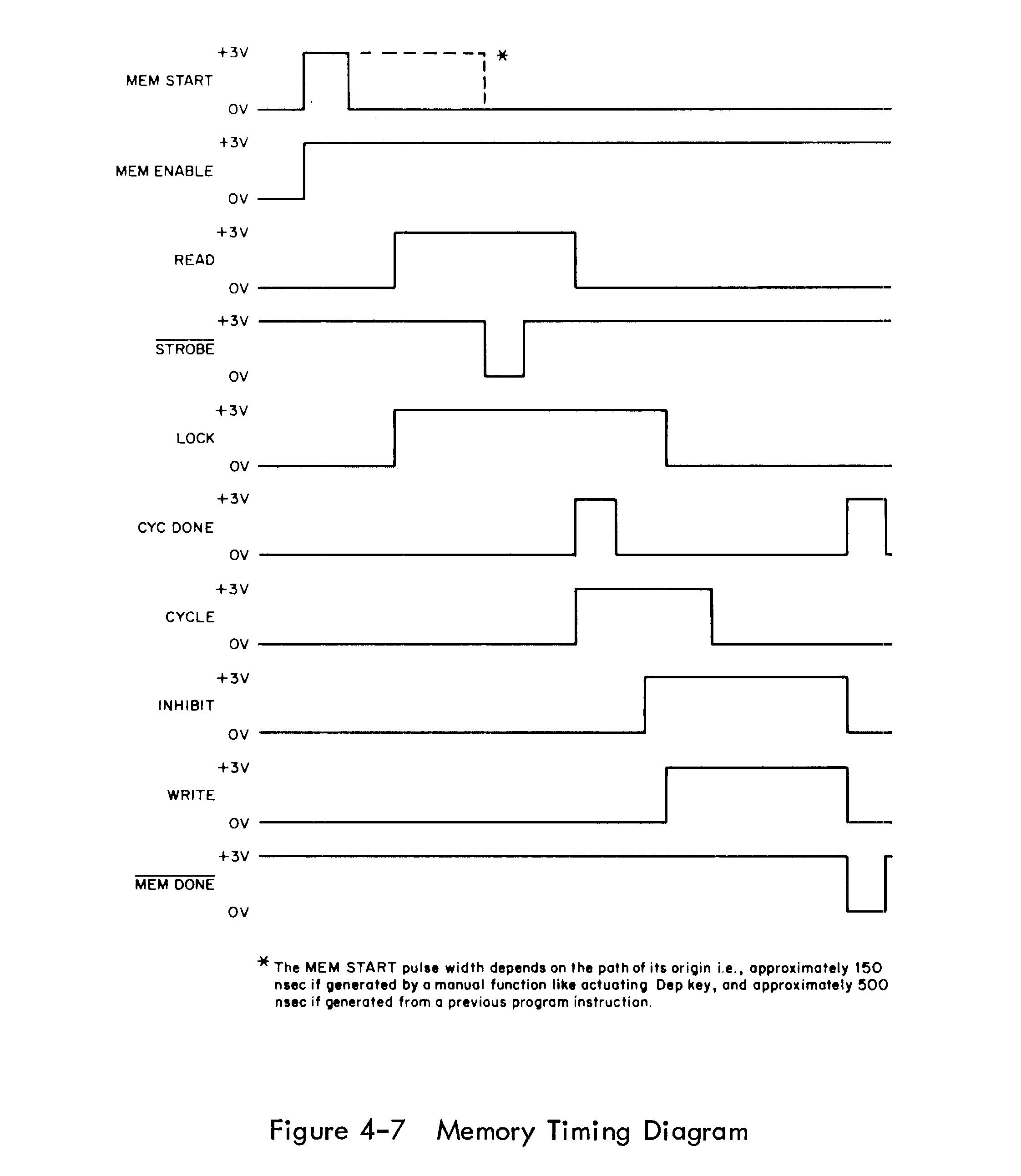

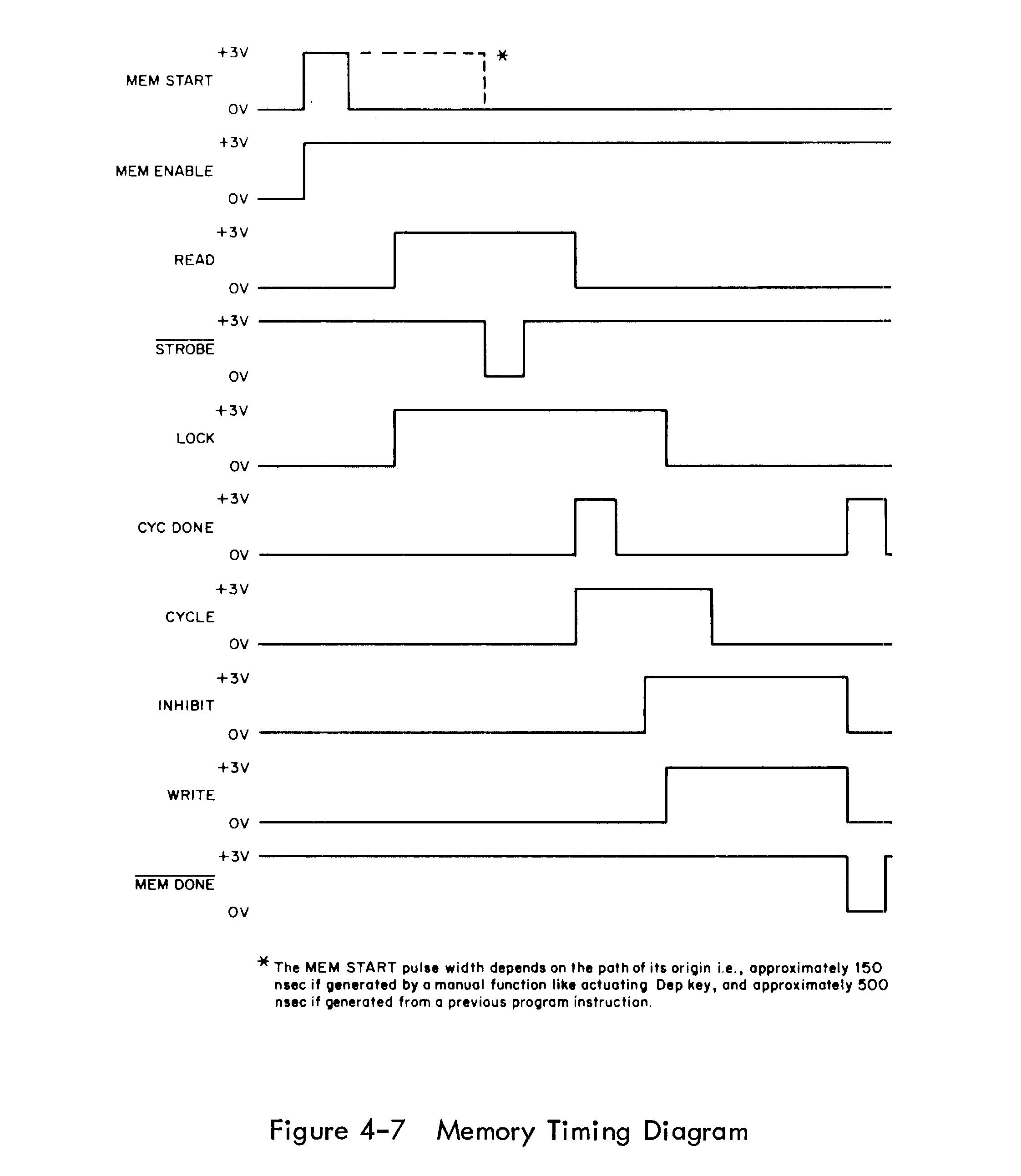

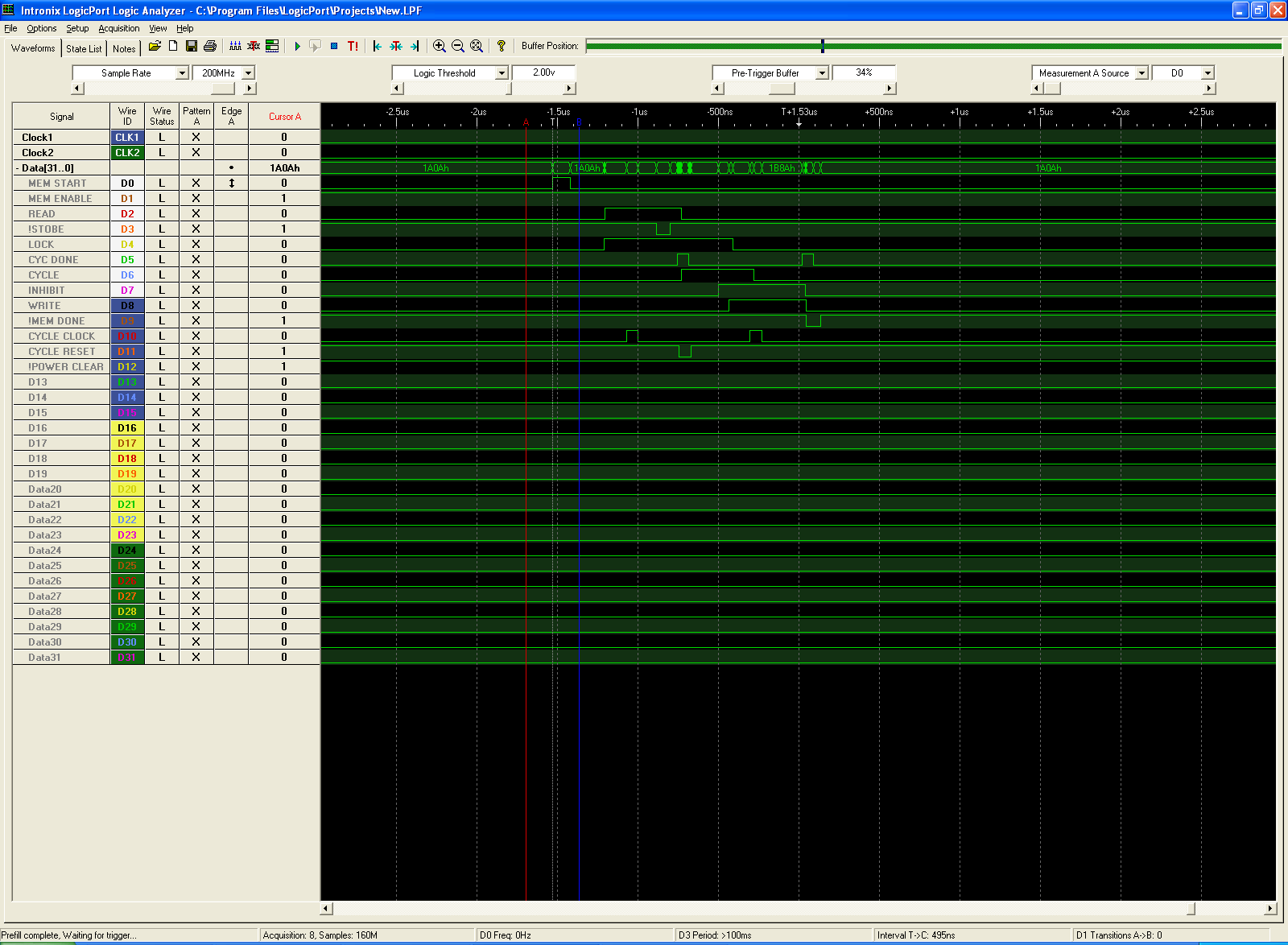

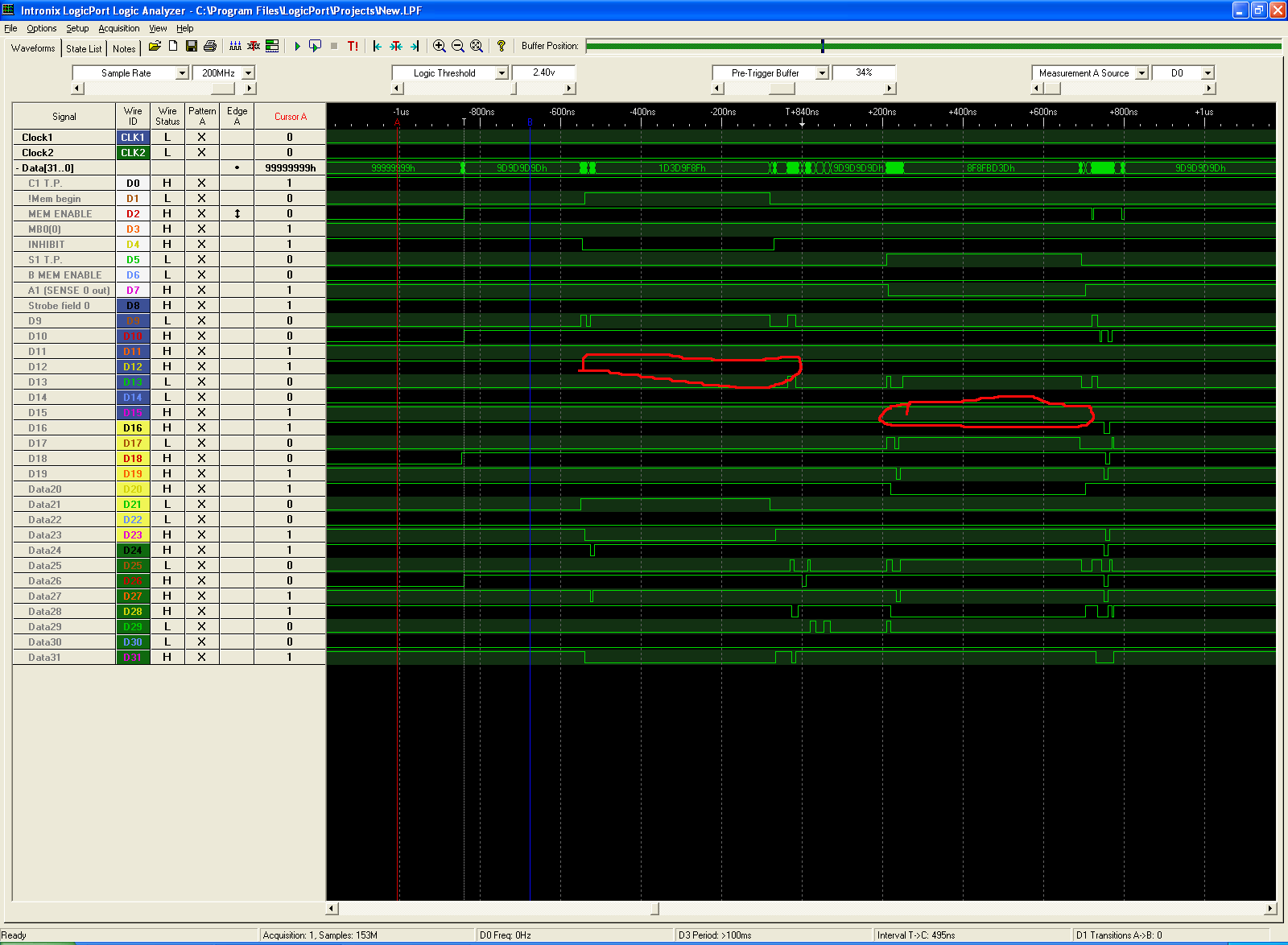

Jag har i helgen gett mig på att mäta lite på mäta på blocket "Memory control". Det generar de signaler som behövs för att göra en minnescykel i maskinen. I korta drag så skickar CPU:n en "MEN START" puls till detta blocket som sedan genererar alla pulser som behövs för att läsa och skriva till minnet och skickar sedan tillbaks en puls för att tala om att minnesoperationen är klar. En cykel startar med läsningen och avslutas alltid med en skrivning eftersom en läsning förstör minnesinnehållet!

Så här ska det se ut (jag tycker mycket om DEC's dokumentation där man hittar dessa diagrammen):

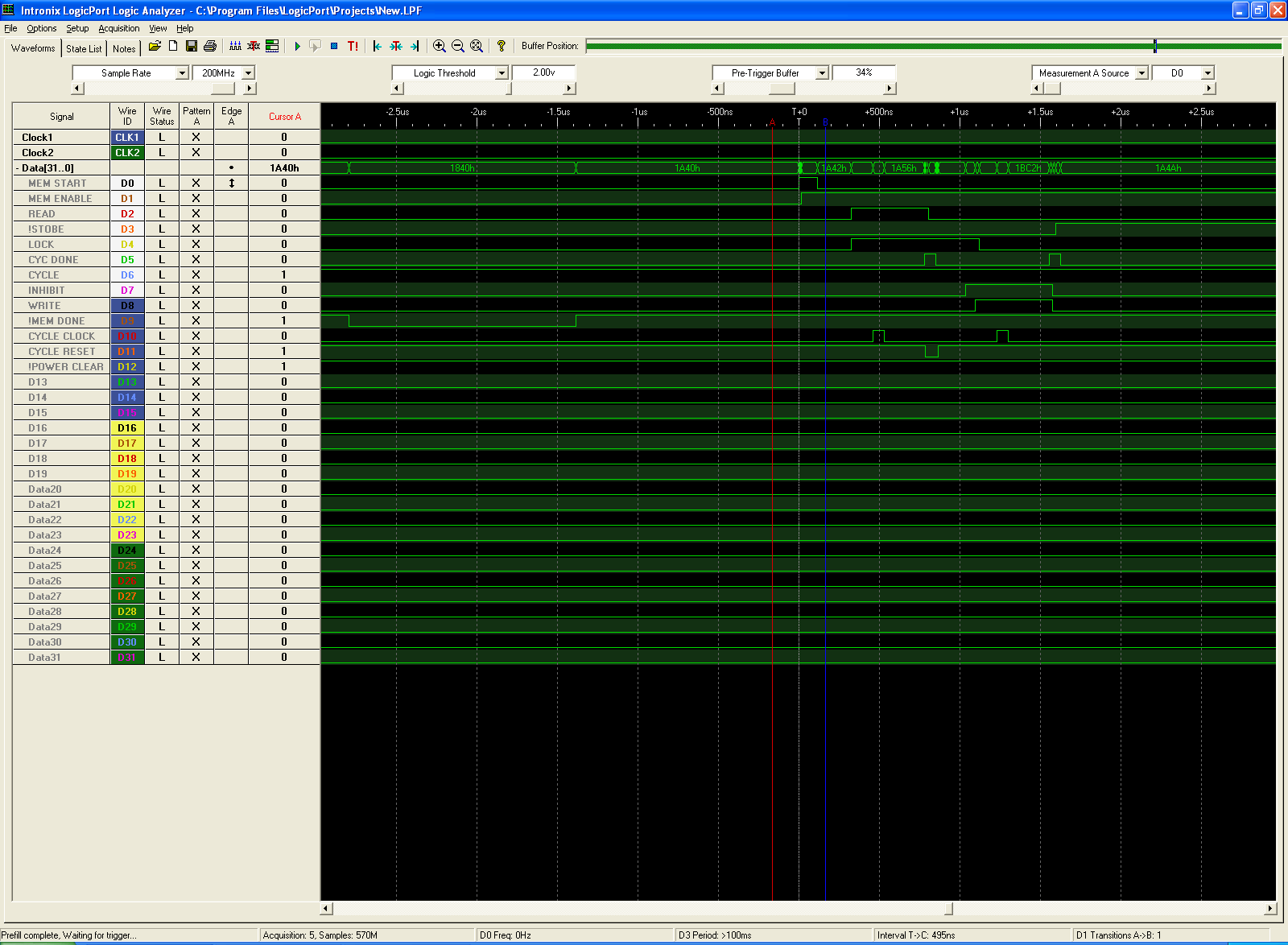

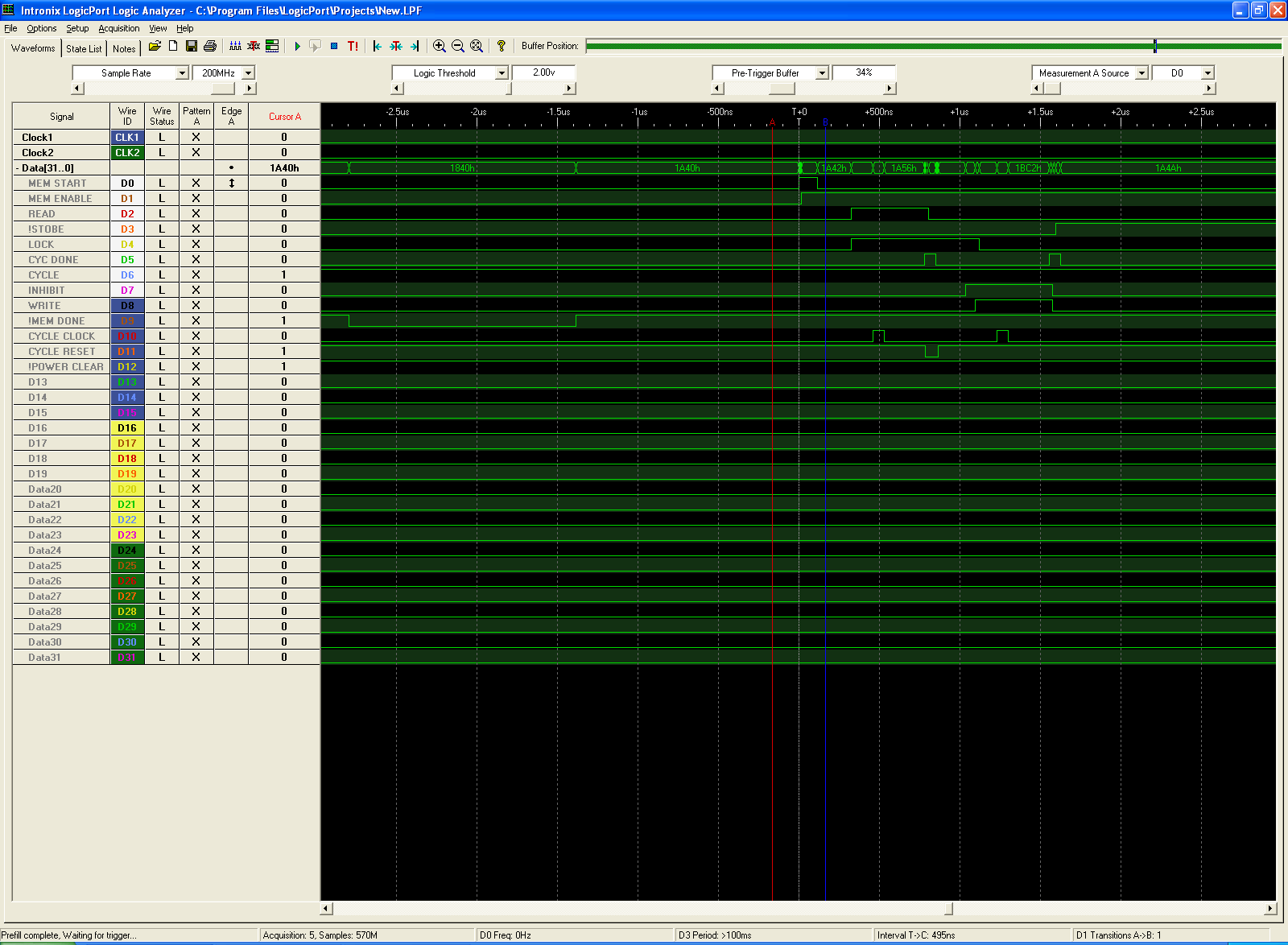

Nedan resultatet av mätningen av samma signaler (logikaren älskar jag nästan mer än dokumentationen (tror jag). Att mäta är att veta!)

Det ser ju inte helt hopplöst ut. Men !MEM DONE kommer innan cykeln startar, !STROBE är konstig och CYCLE är alltid hög.

Detta måste fixas! Sen ska resten av korten runt minnet (som drivkorten till spolarna i minneskärnorna och förstärkarkorten av signalen från kärnorna) tillbaks i maskinen. Sen ska det bli intressant att se om det går att läsa/skriva från minnet!

Jag har i helgen gett mig på att mäta lite på mäta på blocket "Memory control". Det generar de signaler som behövs för att göra en minnescykel i maskinen. I korta drag så skickar CPU:n en "MEN START" puls till detta blocket som sedan genererar alla pulser som behövs för att läsa och skriva till minnet och skickar sedan tillbaks en puls för att tala om att minnesoperationen är klar. En cykel startar med läsningen och avslutas alltid med en skrivning eftersom en läsning förstör minnesinnehållet!

Så här ska det se ut (jag tycker mycket om DEC's dokumentation där man hittar dessa diagrammen):

Nedan resultatet av mätningen av samma signaler (logikaren älskar jag nästan mer än dokumentationen (tror jag). Att mäta är att veta!)

Det ser ju inte helt hopplöst ut. Men !MEM DONE kommer innan cykeln startar, !STROBE är konstig och CYCLE är alltid hög.

Detta måste fixas! Sen ska resten av korten runt minnet (som drivkorten till spolarna i minneskärnorna och förstärkarkorten av signalen från kärnorna) tillbaks i maskinen. Sen ska det bli intressant att se om det går att läsa/skriva från minnet!

- anders_bzn

- Inlägg: 5927

- Blev medlem: 17 december 2008, 19:22:18

- Ort: Kävlinge

- Kontakt:

Re: PDP8 Renovering

Så där ja. Så ska det visst se ut. Ibland är det bra att ta en paus och fundera lite. Efter att ha tittat på resultatet från förra mätningen och jämfört med schemat så var resultatet inte rimligt. Det kunde omöjligen bete sig som det såg.

Nu har jag mätt om på rätt ställen...

Sen har alla drivkorten till kärnminnet åter satts på plats och innan dess mätte jag alla halvledare med multimetern och det verkade friskt. Sen testade jag att göra minnesaccesser, inte något hände. Inte ett litet fladder på någon bit märks så något är riktigt fel.

Så nu har jag fortsatt att mäta styrsignaler på den digitala sidan av de nyligen i satta korten. Ännu så länge har jag inte sett något konstigt. Men det finns flera kvar. Skulle nu inte detta ge något så får jag börja mäta strömmar i spolarna som är i varje kärna. Då skulle det vara bra med en strömprobe och ett minnesoscilloskop. Detta kommer bli dyrt...

- anders_bzn

- Inlägg: 5927

- Blev medlem: 17 december 2008, 19:22:18

- Ort: Kävlinge

- Kontakt:

Re: PDP8 Renovering

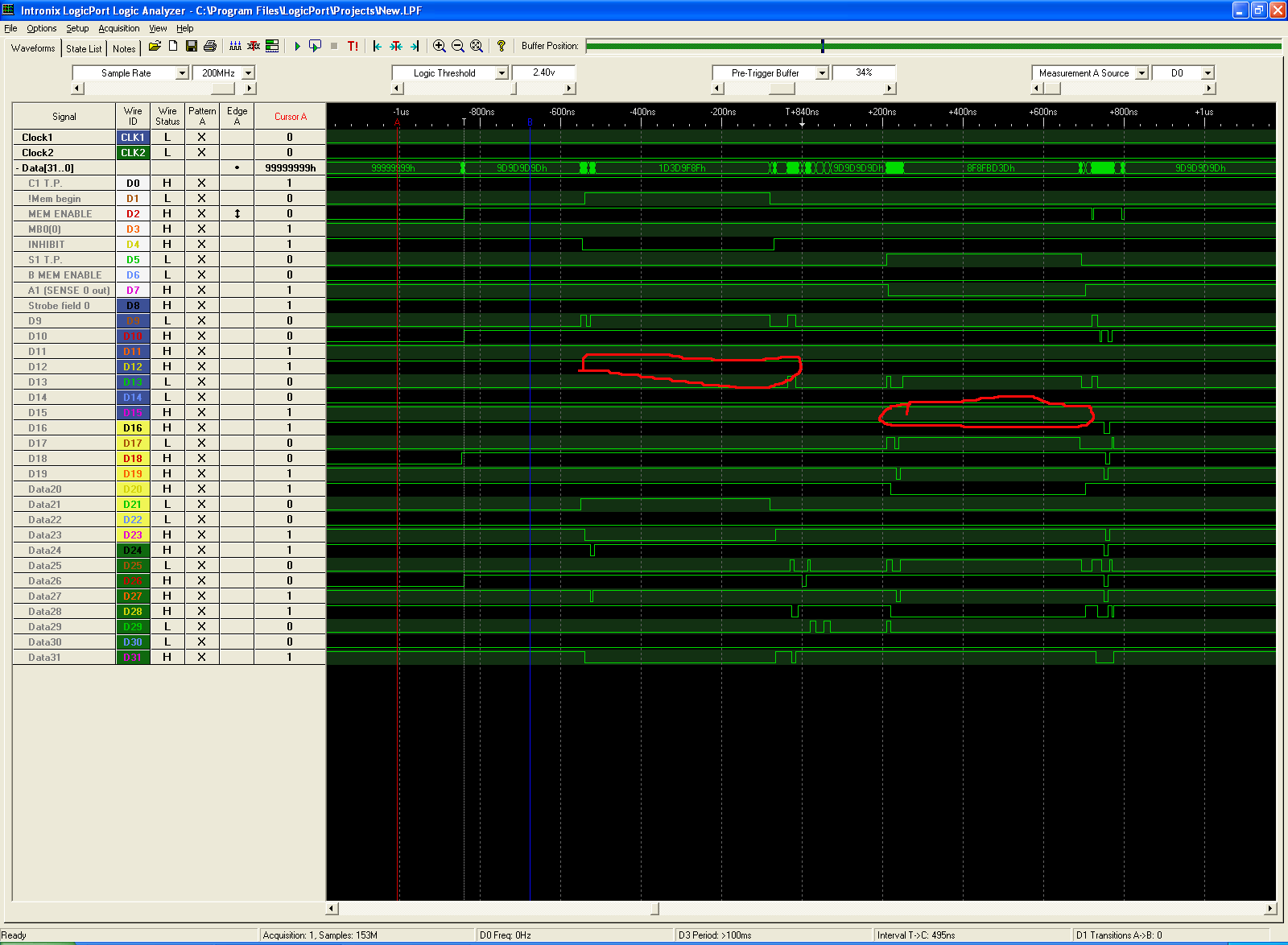

Jag mätte tidigare i veckan på "R/W Source/return switches". Den består av två H-bryggor, en för X och en för Y-lindingarna i kärnminnet. Det är dessa som bestämmer åt vilket håll som strömmen ska gå i X-Y beroende på om man vill läsa eller skriva till minnet. Vilken X respektive Y kolumn som sedan väljs senare av "X-Y selection switches" beroende på vilken adress man vi läsa/skriva till. Kopplingen består av två stycken G228 kort.

Igår orkade jag kolla på mätresultatet:

Där jag har ringat in borde utsignalen från NAND grinden gått låg men det gör den aldrig! Detta gör att ena halvan av H-bryggan aldrig har någon transistor som leder och ingen kärna i arrayen blir någonsin vald. Detta gör att det är omöjligt att göra någon som helst minnesaccess! Nu ska jag bara får en stund i verkstan så ska kretsen bytas, en 7440, två stycken fyra ingångars NAND grindar.

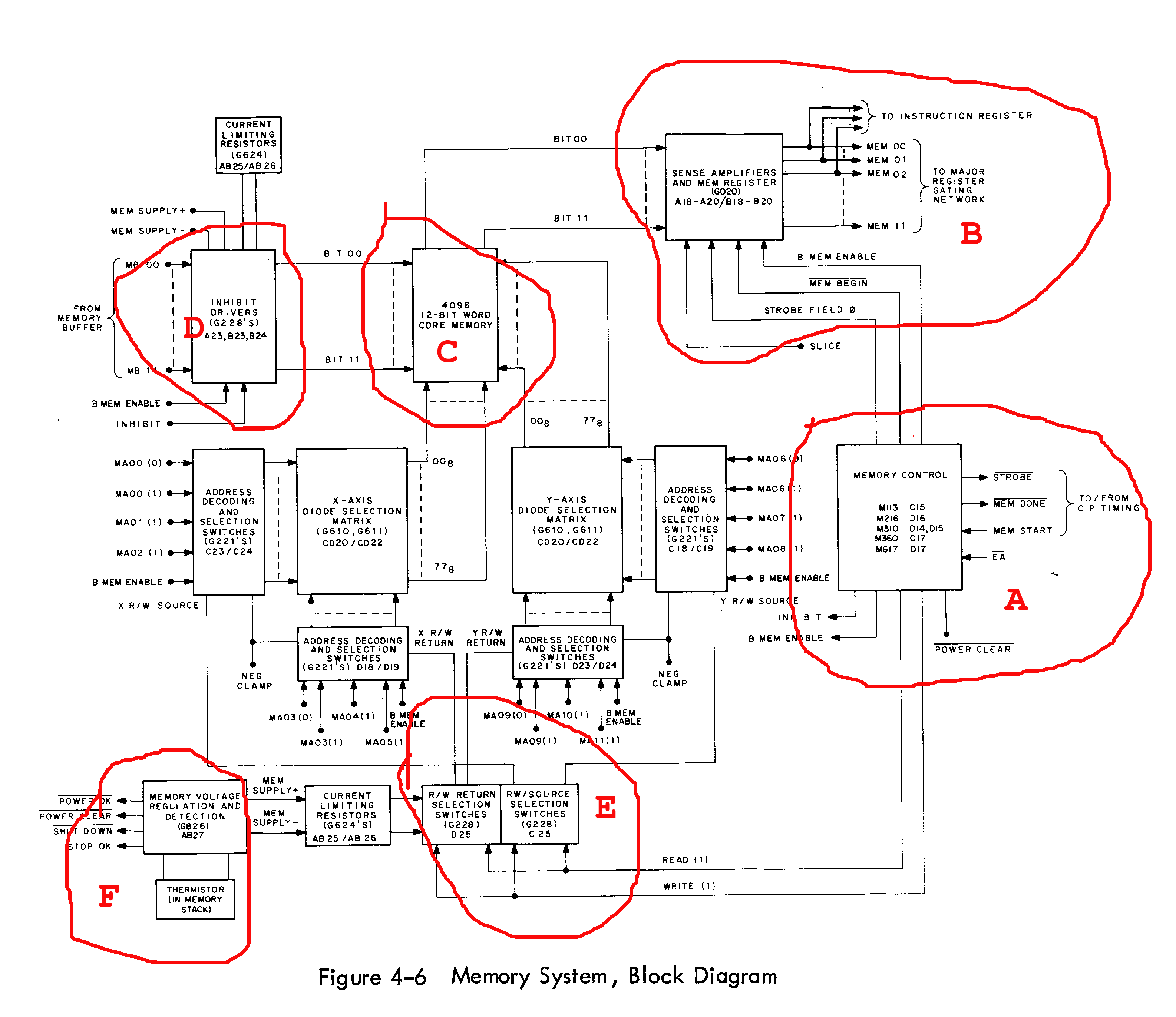

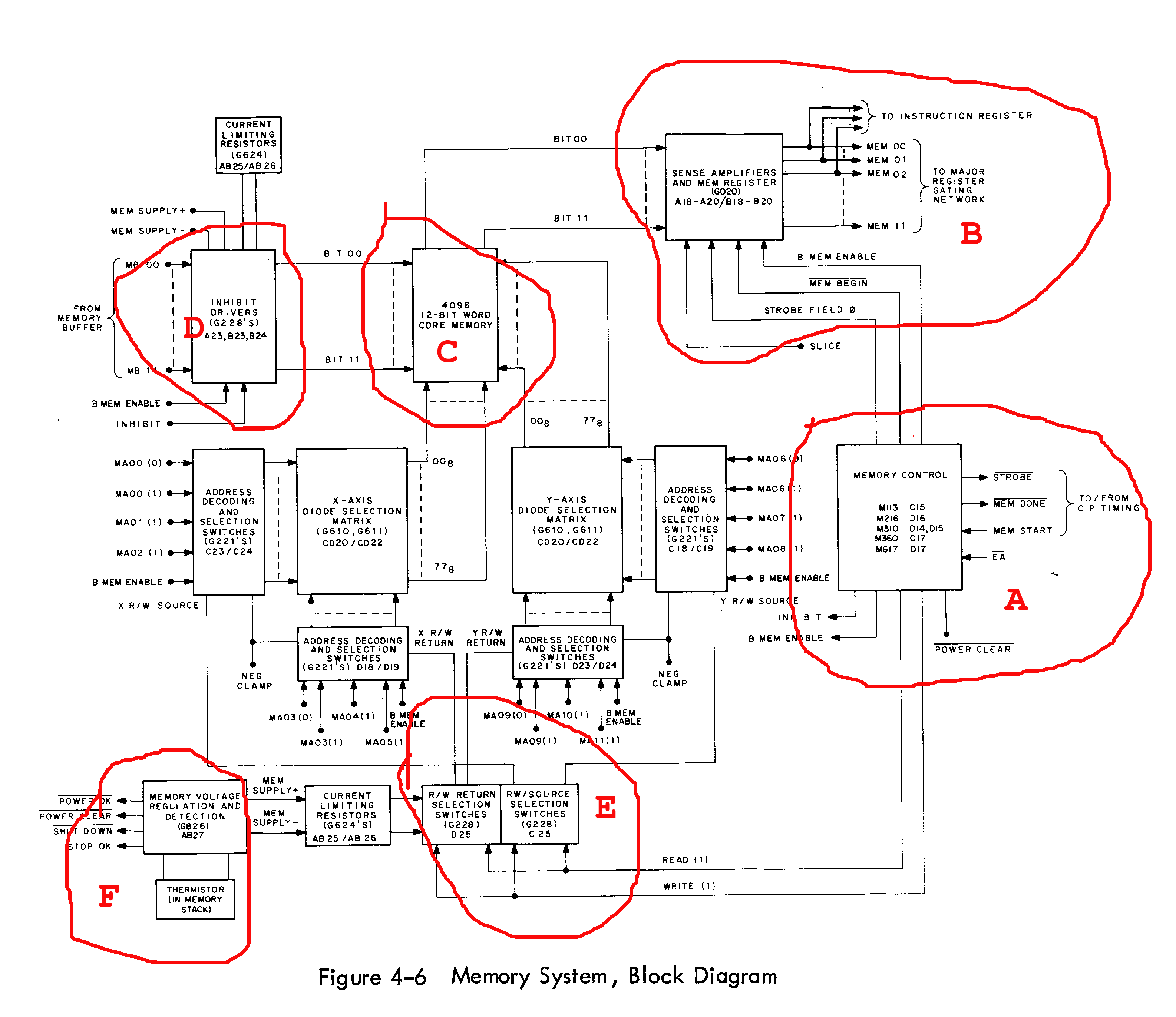

Detta är då Blockdiagrammet för minnessubsystemet

A. Memory control

Detta blocket var det jag mätte på först. Det genererar alla logiska styrsignaler som behövs för att göra en minnescykel.

B.Sense amplifiers

Detta block består av sex stycken G020 kort, det tar signalen från sense-lindningen som går genom samtliga kärnor för en minnesbit (det finns 2 st på varje kort, 12 bitar totalt) och förstärker den och klockar in resultatet i ett register. Dessa går sedan till memmory buffer registret i CPU:n. De tre översta bitarna går även till instruktionsavkodningen. Dessa korten har jag mätt på för två bitar för att kolla om alla digitala signaler fanns där. Det gjorde dom. Har inte mätt på den "analoga" sidan ännu.

C. Core memory.

Själva packen med 12*4096 minnes kärnor.

D. Inhibit drivers.

Drivarna till en lidning som bestämmer om det ska skrivas en etta eller nolla till den utvalda kärnan under skrivcykeln. Här har jag bara mätt de digitala signalerna och de verkar rätt.

E. R/W Source/return switches.

De avan nämnda H-bryggorna. Här verkar det finnas en död 7440 att byta.

F. Memory voltage regulation and detection.

Detta kortet (G826) var ett av det första som jag lagade efter nätaggregatet. Det reglerar minnesspänningen och genererar !POWER OK signalen och !POWER CLEAR signalen. Innan de båda signalerna fungerade som de skulle funkade inget alls i maskinen.

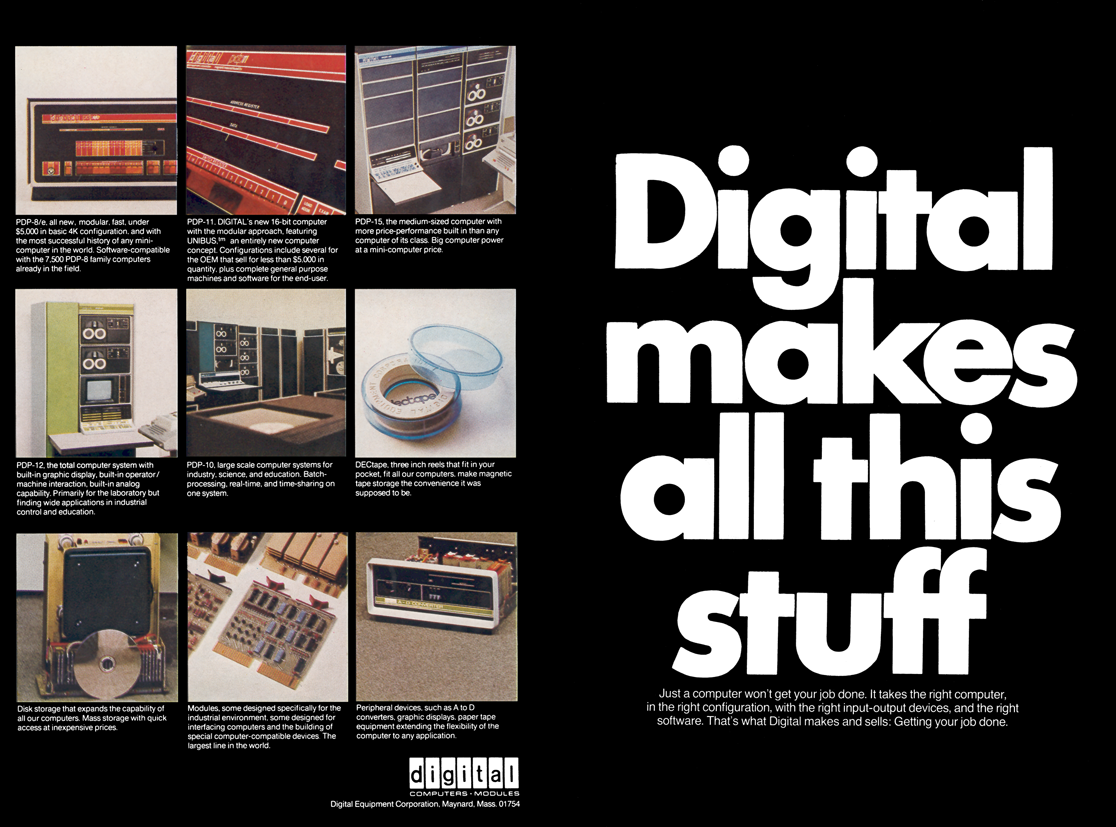

Sen var jag tvungen att lägga upp denna lilla annons om är saxad ur någon gammal tidning på 1970-talets början.

Igår orkade jag kolla på mätresultatet:

Där jag har ringat in borde utsignalen från NAND grinden gått låg men det gör den aldrig! Detta gör att ena halvan av H-bryggan aldrig har någon transistor som leder och ingen kärna i arrayen blir någonsin vald. Detta gör att det är omöjligt att göra någon som helst minnesaccess! Nu ska jag bara får en stund i verkstan så ska kretsen bytas, en 7440, två stycken fyra ingångars NAND grindar.

Detta är då Blockdiagrammet för minnessubsystemet

A. Memory control

Detta blocket var det jag mätte på först. Det genererar alla logiska styrsignaler som behövs för att göra en minnescykel.

B.Sense amplifiers

Detta block består av sex stycken G020 kort, det tar signalen från sense-lindningen som går genom samtliga kärnor för en minnesbit (det finns 2 st på varje kort, 12 bitar totalt) och förstärker den och klockar in resultatet i ett register. Dessa går sedan till memmory buffer registret i CPU:n. De tre översta bitarna går även till instruktionsavkodningen. Dessa korten har jag mätt på för två bitar för att kolla om alla digitala signaler fanns där. Det gjorde dom. Har inte mätt på den "analoga" sidan ännu.

C. Core memory.

Själva packen med 12*4096 minnes kärnor.

D. Inhibit drivers.

Drivarna till en lidning som bestämmer om det ska skrivas en etta eller nolla till den utvalda kärnan under skrivcykeln. Här har jag bara mätt de digitala signalerna och de verkar rätt.

E. R/W Source/return switches.

De avan nämnda H-bryggorna. Här verkar det finnas en död 7440 att byta.

F. Memory voltage regulation and detection.

Detta kortet (G826) var ett av det första som jag lagade efter nätaggregatet. Det reglerar minnesspänningen och genererar !POWER OK signalen och !POWER CLEAR signalen. Innan de båda signalerna fungerade som de skulle funkade inget alls i maskinen.

Sen var jag tvungen att lägga upp denna lilla annons om är saxad ur någon gammal tidning på 1970-talets början.

Re: PDP8 Renovering

Nu verkar det som om du kanske inte behöver mäta strömmar i spolarna, men ett riktigt budgettips för minnesoscilloskop om det är signaler som går att fås att repetera med önskat intervall är att göra någon koppling som tar signalen du vill mäta och mixtrar lite lagom med den så att den går att köra in på videoingången på ett tv-kort (eller grafikkort med tv in). En tv-synkgenerator och lämplig elektronik som kombinerar signalerna är den givna grunden, och i det här fallet skulle fördröjda varianter av tv-synkpulserna kunna kopplas in istället för de manuella knapparna för att skriva till eller läsa från minnet, för att generera antingen 100 eller 15625 läs/skrivcykler per sekund. Lämpligt är väl att mata en sådan tv-synkgenerator från någon klocka i PDP'n för att slippa ytterligare en källa till jitter, fast det är kanske inte särskilt kritiskt. Varje vettigt tv-kort borde hinna ta ett gäng samples under varje klockperiod på en dator som är byggd med standard-TTL.anders_bzn skrev:Så nu har jag fortsatt att mäta styrsignaler på den digitala sidan av de nyligen i satta korten. Ännu så länge har jag inte sett något konstigt. Men det finns flera kvar. Skulle nu inte detta ge något så får jag börja mäta strömmar i spolarna som är i varje kärna. Då skulle det vara bra med en strömprobe och ett minnesoscilloskop. Detta kommer bli dyrt...

- anders_bzn

- Inlägg: 5927

- Blev medlem: 17 december 2008, 19:22:18

- Ort: Kävlinge

- Kontakt:

Re: PDP8 Renovering

Man kan troligen att göra så, men det är ju inte heller någon snabb väg fram. Får väl låna ett skåp på jobbet annars.

Men nu har jag varit ute och bytt kretsen och det FUNGERAR att läsa och skriva till minnet!

Visst bara fem bitar av tolv på vissa adresser men det är ett stort steg framåt. Nu finns det massor att kolla, adressavkodningen, inhibit drivers (som är uppbyggd av tre G228:or som det som jag just lagade) och sense amplifiers. På sense-amplifiers korten sitter det en mycket obsolete IC som påminner om en OP men som är en Core memory amplifier (de finns på Ebay för $10).

Nu är jag GLAD!

Men nu har jag varit ute och bytt kretsen och det FUNGERAR att läsa och skriva till minnet!

Visst bara fem bitar av tolv på vissa adresser men det är ett stort steg framåt. Nu finns det massor att kolla, adressavkodningen, inhibit drivers (som är uppbyggd av tre G228:or som det som jag just lagade) och sense amplifiers. På sense-amplifiers korten sitter det en mycket obsolete IC som påminner om en OP men som är en Core memory amplifier (de finns på Ebay för $10).

Nu är jag GLAD!

Re: PDP8 Renovering

Grattis!!

Det här är en väldigt kul tråd att följa. En av de trådarna jag hajar till och blir ivrig över när jag ser att de uppdaterats

Fascinerande med en dator man kan vara in på sån låg nivå (jag menar detaljer hårdvarumässigt!) och laga och felsöka.

Keep up the good work!

Det här är en väldigt kul tråd att följa. En av de trådarna jag hajar till och blir ivrig över när jag ser att de uppdaterats

Fascinerande med en dator man kan vara in på sån låg nivå (jag menar detaljer hårdvarumässigt!) och laga och felsöka.

Keep up the good work!

- anders_bzn

- Inlägg: 5927

- Blev medlem: 17 december 2008, 19:22:18

- Ort: Kävlinge

- Kontakt:

Re: PDP8 Renovering

Tack!

Kul att tråden roar.

Jag har gjort lite mer framsteg, inte för att det märks inte mycket på funktionen med ändå ett steg framåt. Jag har mätt den digitala biten av alla "inhibit drivers" totalt tre stycken G228. Jag fick vettiga resultat på två av korten, de satt i positionerna jämte varandra. Men det tredje kortet uppförde sig mycket illa. Tillslut insåg jag var det var, förlängningskortet förlänger två kortplatser i detta fallet även en tom plats. Inte bra, det var som att stoppa en massa antenner ner i bakplanet. Denna tomma positionen har signaler för ytterligare ett "inhibit driver" kort som används om man har minne med paritet vilket jag inte har...

Skönt när saker får en förklaring.

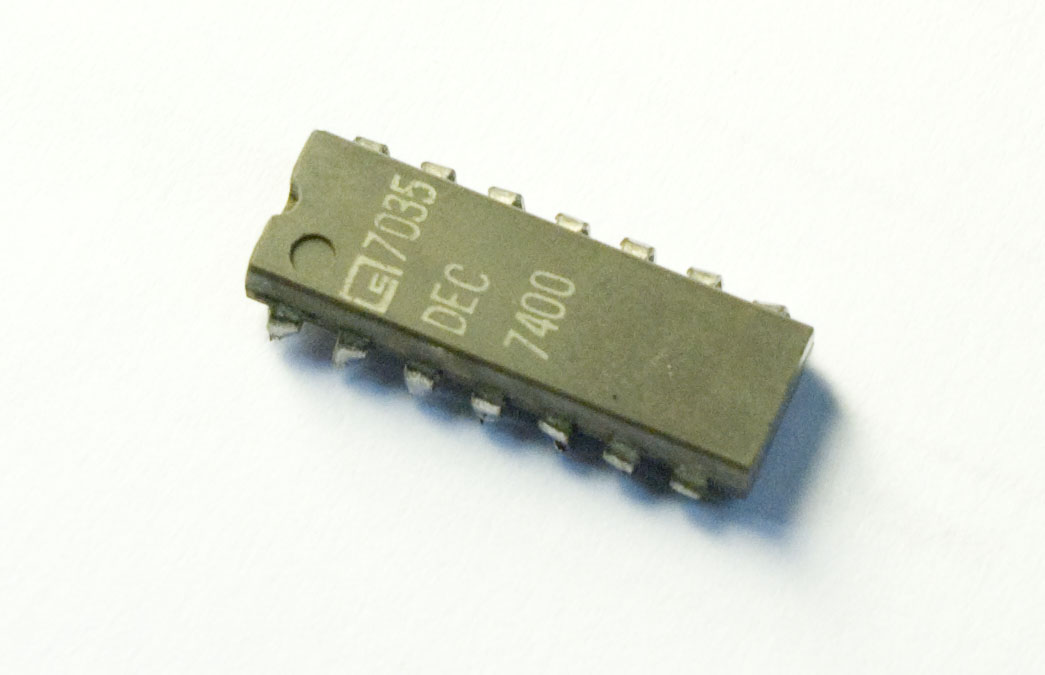

Sen började jag mäta på korten för "memory selection" G221 och hittade en 7400 som hade en av sina utgångar låg oberoende av ingångarnas värde, så den blev bytt. Märkligt att dessa gråa kretsar är klart överrepresenterade bland de trasiga. Den leverantören skulle jag inte valt...

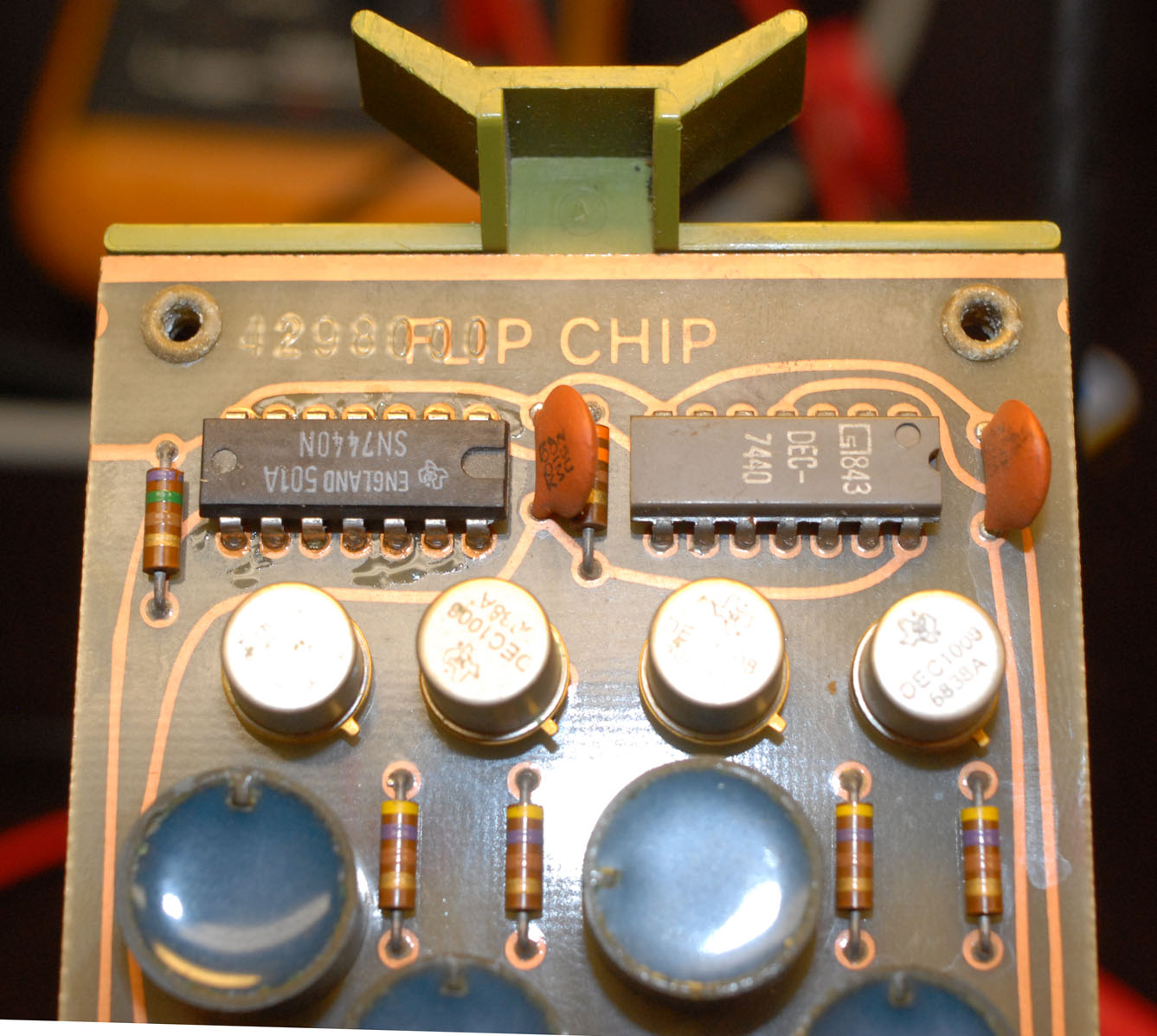

Detta är den trasiga kretsen!

Detta är det trasiga kortet (G228) som jag lagade i helgen, notera den bytta vänstra kretsen. Den var tidigare en av de ökända gråa...

Kul att tråden roar.

Jag har gjort lite mer framsteg, inte för att det märks inte mycket på funktionen med ändå ett steg framåt. Jag har mätt den digitala biten av alla "inhibit drivers" totalt tre stycken G228. Jag fick vettiga resultat på två av korten, de satt i positionerna jämte varandra. Men det tredje kortet uppförde sig mycket illa. Tillslut insåg jag var det var, förlängningskortet förlänger två kortplatser i detta fallet även en tom plats. Inte bra, det var som att stoppa en massa antenner ner i bakplanet. Denna tomma positionen har signaler för ytterligare ett "inhibit driver" kort som används om man har minne med paritet vilket jag inte har...

Skönt när saker får en förklaring.

Sen började jag mäta på korten för "memory selection" G221 och hittade en 7400 som hade en av sina utgångar låg oberoende av ingångarnas värde, så den blev bytt. Märkligt att dessa gråa kretsar är klart överrepresenterade bland de trasiga. Den leverantören skulle jag inte valt...

Detta är den trasiga kretsen!

Detta är det trasiga kortet (G228) som jag lagade i helgen, notera den bytta vänstra kretsen. Den var tidigare en av de ökända gråa...