Sida 1 av 2

Dividera Med 8 ?

Postat: 10 oktober 2023, 22:30:34

av 4kTRB

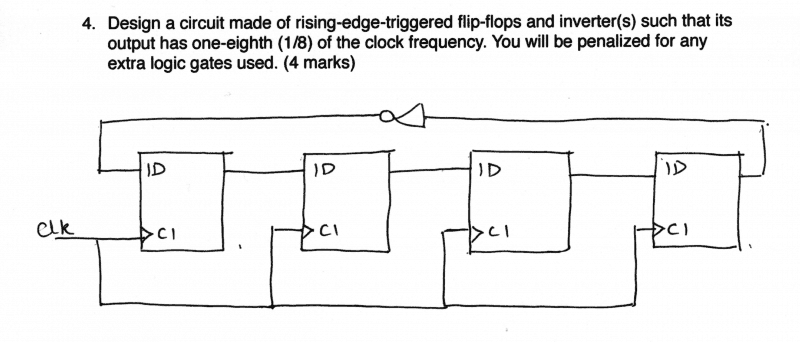

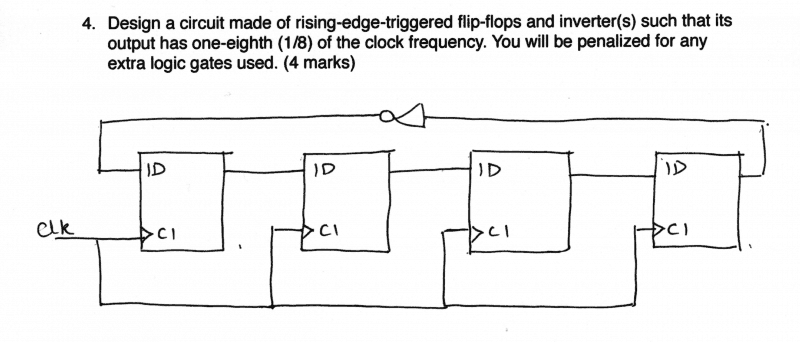

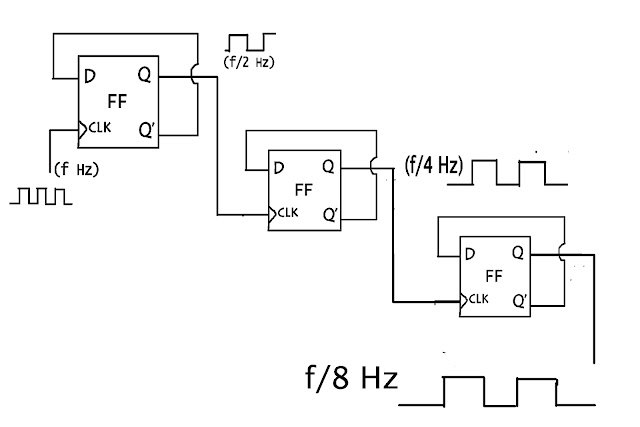

Såg den här enkla kretslösningen för att dela med 8.

Infrekvensen ska vara 14MHz men vilken logikfamilj klarar detta eller mer relevant - vilken logikfamilj är lämpligast?

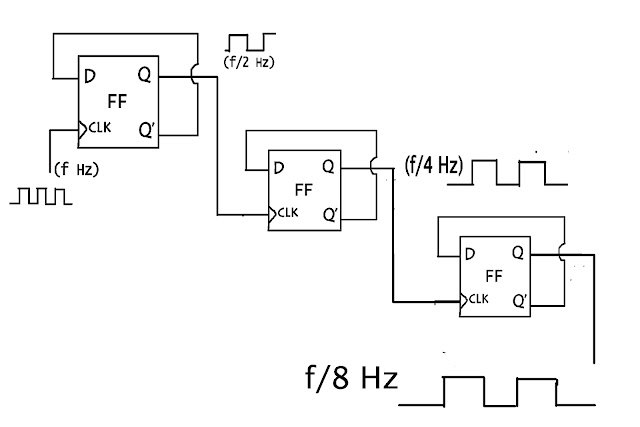

Sett även den här...

Re: Dividera Med 8 ?

Postat: 11 oktober 2023, 02:19:42

av Synesthesia

För 5V: 74HC, 74HCT, 74LS.

Re: Dividera Med 8 ?

Postat: 11 oktober 2023, 09:33:38

av guckrum

Den första kretsen förutsätter väl någon form av reset om den skall dela med åtta?

Den första kretsen är synkron, dvs alla klockade element är kopplade till samma klocka. Den andra är asynkron, där "datasignaler" kopplas in på klockorna. I 99.99% av alla designer vill man jobba synkront, dvs enligt övre bilden. I de fall man inte vill det så har man en bra anledning som man kan argumentera för. Asynkrona designer kan fungera bra när det är enkla, som i bilden, men de är mycket svåra att felsöka och bygga vidare på, eftersom olika element klockas vid olika tidpunkter. Usch!

Re: Dividera med annat än 8

Postat: 22 oktober 2023, 20:24:10

av alexanderson

Om frågeställaren hade velat dela med 3 eller 5 eller 7. Hur hade Er lösning sett ut ?

Re: Dividera Med 8 ?

Postat: 22 oktober 2023, 22:19:41

av guckrum

Synkron tillståndsmaskin. Två alt tre vippor samt lite logik.

Re: Dividera Med 8 ?

Postat: 22 oktober 2023, 22:24:14

av 4kTRB

Samma logikfamiljer hade nog blivit svaret.

Re: Dividera Med 8 ?

Postat: 23 oktober 2023, 09:33:04

av HUGGBÄVERN

CD4017

Re: Dividera Med 8 ?

Postat: 23 oktober 2023, 10:02:00

av Mickecarlsson

Jupp, 4017 med utgång 9 till reset.

EDIT: för första exemplet,

För de andra, utgång 4, 6 eller 8 till reset

Re: Dividera Med 8 ?

Postat: 23 oktober 2023, 10:08:22

av Mickecarlsson

Re: Dividera Med 8 ?

Postat: 23 oktober 2023, 17:10:40

av Icecap

Första schema kräver att det utförs en reset i samband med power-on.

En 4017 är ju asynkron och om den fungerar beror på timingskrav.

Faktisk är timingkraven det avgörande för att välja lösning.

Re: Dividera Med 8 ?

Postat: 23 oktober 2023, 17:59:49

av Marta

Lösningar med att återkoppla en asynkron reset är inget bra. En synkron räknare med synkron reset eller vippor och grindar som ger rätt delning är det stabilaste. Johnsonräknaren i första exemplet är bra om något skall avkodas glitchfritt. Där ändras endast en vippa för varje klockpuls.

Det finns räknare som kan sättas synkront. Med en sådan och en grind som känner av när den står på noll och då ger signal så nästa klocka sätter räknaren är nog det enklaste när det behövs udda delningstal.

Re: Dividera Med 8 ?

Postat: 24 oktober 2023, 05:59:48

av MiaM

Med t.ex. 4017 eller liknande så kan man få utgången synkron genom att köra signalen genom t.ex. en halv 74xx74 som klockas med ingångsklockan. (Förutsatter att vald 74xx74 är snabb i förhållande till 4017, eller enklare att 74xx74 klockas på omvänd flank jämfört med 4017)

Re: Dividera Med 8 ?

Postat: 24 oktober 2023, 09:10:17

av HUGGBÄVERN

Nu får man väl plocka fram läroboken i kombinatorik.

Re: Dividera Med 8 ?

Postat: 24 oktober 2023, 09:26:22

av guckrum

Det kan fungera, men det brister i modern designmetodik och inget som man bör lära ut till någon på 2020-talet. Det fanns en tid när man inte hade så många transistorer på kiselbrickan för en rimig peng, och då var man tvungen att vara ingenjörsmässigt kreativ/finurlig/listig och lösa sitt problem med de bitar/kretsar som fanns.

Att designa asynkront är dålig metodik för att det krävs "specialare" för att det skall fungera, typ "7474 måste vara snabb jämfört med 4017" (det syns ju inte i schemat om ingen präntat dit det i klartext) eller att en av alla kretsar i konstruktionen klockas på omvänd flank osv. Kan fungera för one-offs (och det kan mycket väl vara helt okej i specifika fall), men det är inget som skalar säkert över storlek, logikfamilj, temperatur etc. (Se tex schemat på kaskadkopplingen i databladet för 4017. Varje ny 4017 i kaskaden får en fördröjd output jämfört med föregående, och utsignalerna kommer att överlappa med glitchar och skit som följd om man bygger någon avkodare baserad på dem. Urk.)

Synkron design, å andra sidan, innebär att alla klockade element går på precis samma klocka och samma flank. Då minimerar man alla möjliga synkroniseringsproblem till det enda problemet att distribuera klockan till alla enheter samtidigt. Det kan vara svårt nog, men det är bara ETT problem att lösa, istället för okänt antal asynkrona temperaturberoende hickups, glitchar, violeringar av setup och holdtider, metastabilitet osv. All modern digital elektronik (med mycket få specialundantag) är baserade på denna metodik.

74x163 är helt synkron, använd gärna den. Det är en fyrabitarsräknare, så den kräver antagligen några extra grindar för att avkoda en nollställningssignal om man vill räkna modulo N, men designen kommer att vara vattentät.

Re: Dividera Med 8 ?

Postat: 24 oktober 2023, 10:02:18

av MadModder

74163 säger du… såna har jag nog.

När jag läste ’violering’ tänkte jag att nu har väl svengelskan nått sin topp, men violera har ju faktiskt funnits i ordboken sen åtminstone 1500-talet. Tänka sig.